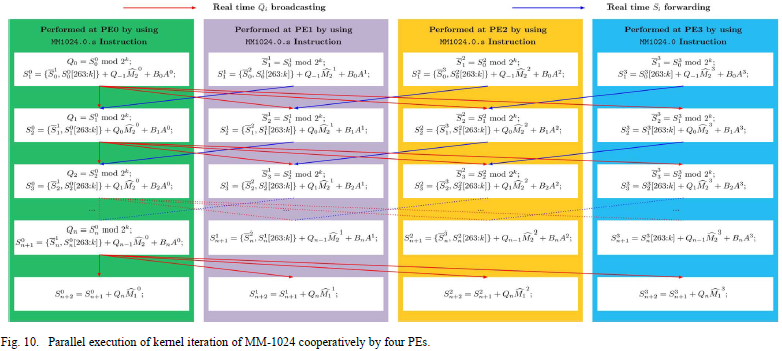

從雲計算、高速率實時通信等應用需求出發,實驗室曾曉洋教授課題組提出了一種異構多核公鑰密碼處理器架構🫴🏿。公鑰密碼算法具有運算任務密集🌡,控製任務簡單的特點,而其中包含的長整數運算是當前各類處理平臺難以解決的技術難點#️⃣。課題組提出的異構多核處理器設計可以實現分布計算和集中控製的機製👨🏼🔬,多個處理單元(PE)並發完成高強度計算任務,而一個通用RISC處理器集中完成的算法的頂層控製與調度。每個處理單元配備高性能的可擴展模乘器🧝🏼♂️,通過模乘器的並行協作實現了靈活高效的大整數模乘運算。因此該架構有效地解決了任務需求與硬件特性的適配問題🅿️,大幅度改善了公鑰密碼處理的性能。課題組提出的異構多核處理器也基於TSMC 65nm LP CMOS工藝進行了邏輯綜合與物理設計。結果表明該多核處理器滿足了高吞吐率🪦、低延遲的工作需求,其工作頻率可達960MHz🍡,1024-bit RSA加密性能可達11548次每秒,256-bit ECC加密性能可達12203次每秒🫦🫏,單次RSA🚵🏻♂️,ECC計算的延遲時間僅為0.087ms 和0.082ms🤟🏼。與已發表的國際同類工作相比,該多核處理器的密碼運算性能達到國際先進水平😮💨,成果“A Heterogeneous Multicore Crypto-Processor With Flexible Long-Word-Length Computation”發表在IEEE Transactions on Circuits and Systems I:Regular Papers上🔈。