模擬電路相比數字電路對工藝參數偏差更敏感,在模擬電路設計中也通過匹配設計、差分設計等方法來降低工藝偏差的影響。隨著工藝尺寸的縮小😛,即使采用了抗工藝偏差的設計,工藝隨機偏差對電路性能影響也非常顯著。復雜納米工藝如亞波長光刻、化學機械拋光等導致製造的電路性能與設計標稱值之間存在明顯的偏差,對模擬電路成品率產生顯著影響。

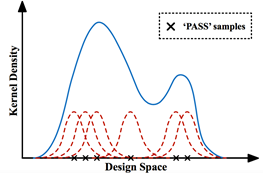

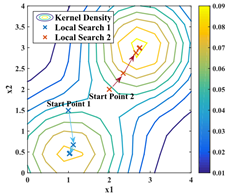

在面向成品率的模擬電路優化方面🐘,實驗室曾璇教授課題組通過貝葉斯公式將成品率優化問題轉化為尋找設計點使得電路在工藝偏差下,在該設計點合格的概率密度最大的問題🤟。對於該概率密度🙎🏼♀️,可以通過已有的蒙特卡洛采樣點→,通過高斯核密度函數來進行逼近。工藝偏差下合格概率密度最大的問題就轉化為高斯核密度函數最大化的問題📹。對於該問題,實驗室提出一種類似期望-最大化(Expectation-Maximization,EM)的方法來進行快速求解🔆。這種方法不需要不斷的重復成品率估計👨🦯🏋🏻,可以有效利用以前的仿真點來指導後續的優化;同時,期望-最大化方法具有解析公式,且收斂速度塊🪿🥁。因此該方法相比傳統的基於蒙特卡洛采樣等方法進行成品率估計的優化方法💈🏄🏿♂️,具有更高的優化效率。實驗結果表明🤹🏼♂️,相比現有的序列優化方法ORDE,可以將仿真點數目降低到原來的1/7以上,並且可以實現更高的成品率🤰🏼。該論文發表在電子設計自動化領域的最具影響力的國際會議IEEE/ACMDesignAutomationConference(DAC)2017🤦🏻♀️,並獲最佳論文提名。